一、设计目的:

1. 通过3-8译码器的设计,掌握组合逻辑电路的设计方法:

- 首先,需要理解3-8译码器的基本功能,即它可以将3位二进制输入(通常表示为A、B、C)转换为8个独立的输出(Y0至Y7),每个输出对应一个特定的二进制码组合。

- 设计过程包括:

a. 确定输入和输出的逻辑关系,即每个输出在什么输入条件下为高电平(1)或低电平(0)。

b. 使用真值表来表示这些逻辑关系。

c. 根据真值表,使用卡诺图或布尔代数简化逻辑表达式。

d. 将简化的逻辑表达式转换为逻辑门电路图,包括与门、或门和非门等。

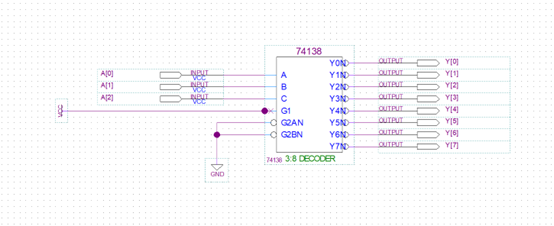

e. 使用逻辑门或集成电路(如74LS138)来实现电路。

2. 掌握组合逻辑电路的静态测试方法:

- 静态测试是指在电路不工作时进行的测试,目的是验证电路的逻辑功能是否正确。

- 测试步骤包括:

a. 根据设计图搭建电路。

b. 使用逻辑探针或万用表检查电路的每个输入和输出,确保它们在所有可能的输入组合下都符合预期。

c. 对于3-8译码器,这意味着检查每个输出是否在正确的输入组合下变为高电平,而在其他组合下为低电平。

d. 记录测试结果,并与理论值进行比较,以确保电路的正确性。

3. 初步了解可编程器件设计的全过程:

- 可编程器件(如FPGA或CPLD)允许用户通过编程来实现特定的逻辑功能,而不是通过物理连接逻辑门。

- 设计过程通常包括:

a. 使用硬件描述语言(如VHDL或Verilog)编写逻辑描述。

b. 使用EDA工具(电子设计自动化工具)进行仿真,以验证逻辑的正确性。

c. 将设计综合到可编程器件中,这通常涉及将硬件描述转换为器件的配置文件。

d. 在实际硬件上进行布局和布线,以确定逻辑元素在器件中的物理位置。

e. 下载配置文件到可编程器件,并进行功能测试,以确保设计按预期工作。

二、设计内容:

1.打开Quartus II软件。

2.创建新工程:选择File/New Project Wizard,指定工作目录(确保路径无中文),设置工程名、顶层设计实体名称,确保三者名称一致,均为英文字母组合。

3.添加设计文件:如果有现成的VHDL或原理图文件,可在此步骤添加;否则,点击“Next”稍后添加。

4.选择FPGA器件:Family选择ACEX1K,Available devices选EP1K30TC144-3,或根据需要选择其他器件。

5.选择外部工具:默认使用Quartus II自带的综合器、仿真器和时序分析器,不做额外选择。

6.完成工程设置:检查工程设置统计窗口,确认无误后点击“Finish”。

7.建立原理图文件:选择File/New/Block Diagram/Schematic File。

8.保存并添加原理图文件到工程:保存文件,确保文件名与工程名一致。

9.开始原理图设计:在原理图上进行设计。

10.添加器件并连线:双击原理图空白处添加器件,连线时避免结点,修改端口名称为A, B, C和Y0-Y7。

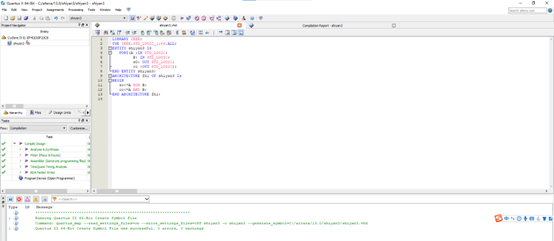

11.预编译:选择Processing/Start/Start Analysis&Synthesis进行综合,如有错误进行定位和修正。

12.添加管脚信息:综合完成后,选择Assignments/Pin Planner分配引脚。

13.为节点分配引脚:双击Location空白处选择对应引脚。

14.全局编译:选择Processing/Start Compilation进行编译。

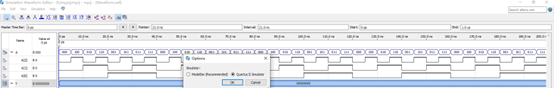

15.创建波形文件:选择File/New/Other Files/Vector Waveform File,添加需要验证的引脚,设置信号值和周期。

16.设置仿真:在Assignments中选择Settings,设置Function类型仿真,将波形文件作为仿真输入。

17.生成网表并进行功能仿真:点击Processing ->Generate Functional Simulator Netlist,然后点击Start Simulator进行仿真,验证逻辑功能。

三、设计过程:

-

理解3-8译码器功能:

- 3-8译码器接受3位二进制输入(A、B、C),并根据输入的不同组合激活8个输出(Y0至Y7)中的一个。

- 输出Y0至Y7对应于输入的二进制编码,例如输入为000时,Y0输出高电平,其他输出为低电平。

-

设计逻辑表达式:

- 根据3-8译码器的功能,可以列出真值表,表示每个输出在不同输入组合下的状态。

- 使用卡诺图或布尔代数简化每个输出的逻辑表达式。

-

实现逻辑电路:

- 根据简化的逻辑表达式,设计逻辑电路图。

- 通常使用与门和非门来实现3-8译码器,因为每个输出都是输入的特定组合的逻辑与。

-

使用硬件描述语言(HDL)编写代码:

- 如果使用FPGA或CPLD等可编程逻辑器件,需要使用VHDL或Verilog等硬件描述语言编写代码。

- 代码应描述输入、输出以及它们之间的逻辑关系。

-

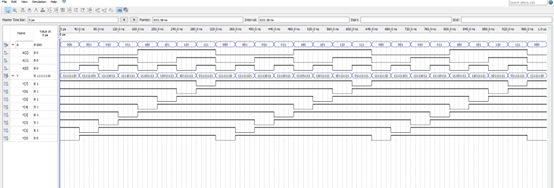

仿真验证:

- 使用仿真工具(如Quartus II中的仿真器)对HDL代码进行仿真,以验证逻辑的正确性。

- 仿真时应覆盖所有可能的输入组合,确保输出符合预期。

-

综合和布局布线:

- 将HDL代码综合成目标器件的网表。

- 进行布局布线,将逻辑映射到实际的物理器件上。

-

下载到硬件进行测试:

- 将设计下载到FPGA或CPLD等硬件上进行实际测试。

- 使用逻辑分析仪或示波器等工具检查输出是否与输入的二进制编码相对应。

-

调试和优化:

- 如果在测试中发现问题,需要回到设计阶段进行调试。

- 根据测试结果对设计进行优化,以提高性能或减少资源使用。

四、设计结果与分析:

仿真环境:

仿真效果:

仿真电路设计

最终效果:

4.1 设计结果:

当输入为000时,只有第一个输出(通常标记为Y0)应该是高电平,其余输出应为低电平。

当输入为001时,只有Y1应该是高电平,其余为低电平。

当输入为111时,只有Y7应该是高电平,其余为低电平。

4.2 设计分析:

设计阶段根据38译码器的真值表设计电路图,构建阶段使用逻辑门(如AND、OR、NOT门)在面包板上构建电路,测试阶段为输入引脚提供不同的二进制信号,并观察输出,分析阶段,根据输出结果验证电路的正确性。

五、思考

为什么在功能仿真时输入设置的周期为2倍的关系?

通过设置较长的周期,仿真可以观察到电路在较长时间内的稳定性和时序行为。这有助于检测潜在的时序问题,如建立时间(setup time)和保持时间(hold time)违规。

仿真整个系统可能需要很长时间,特别是当系统复杂时。通过增加输入信号的周期,可以在不显著影响仿真结果的情况下减少仿真的总时间。

在某些情况下,增加输入信号的周期可以模拟最坏情况下的电路行为,这有助于确保设计在极端条件下也能正常工作。

在某些仿真中,较短的周期可能会引入噪声或随机性,这可能会掩盖设计中的实际问题。增加周期可以减少这些因素的影响,使仿真结果更加可靠。

评论(0)

您还未登录,请登录后发表或查看评论